Research

My graduate research is in the area of power electronics with Prof. Robert Pilawa at UC Berkeley. The theme for power electronics research is always to build more efficient and smaller power converters for applications such as EV, solar, data center, consumer electronics etc.

The main topics I have studied in my graduate research are:

- High performance Flying Capacitor Multilevel (FCML) converter. I’ve designed FCMLs for dc-dc buck and boost, single-phase inverter, single-phase PFC, single-phase active buffer, and three-phase PFC

- Single-phase PFC and active buffer topology, control, and system optimization

- USB-C flyback converter input capacitor reduction with active buffer

- Hybrid switch capacitor dc-dc

My full publication list can be found on Google Scholar:

Below are some of the converters I’ve worked on since I started grad school in 2015:

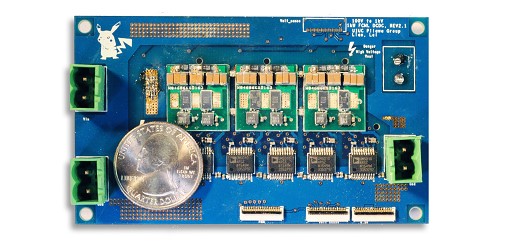

100V-to-1kV 1kW multilevel boost converter – 2016

The converter boosts 100 Vdc to 1 kVdc. The flying capacitor multilevel boost converter utilizes high energy density ceramic capacitors and low-voltage devices to achieve high efficiency and power density. The high efficiency of 94% and power density 330 W/in3 are much higher than state-of-the-art high step-up converter solutions.

Read more: personal version of TPEL2018, UIUC master thesis

Official IEEE publications: ECCE2016, TPEL2018

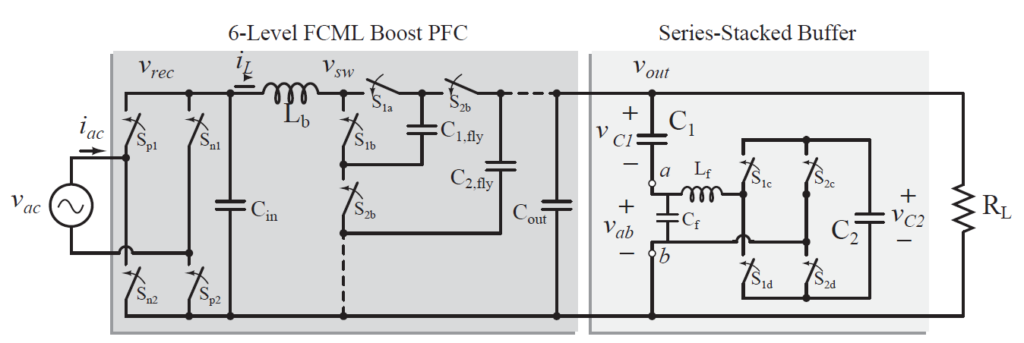

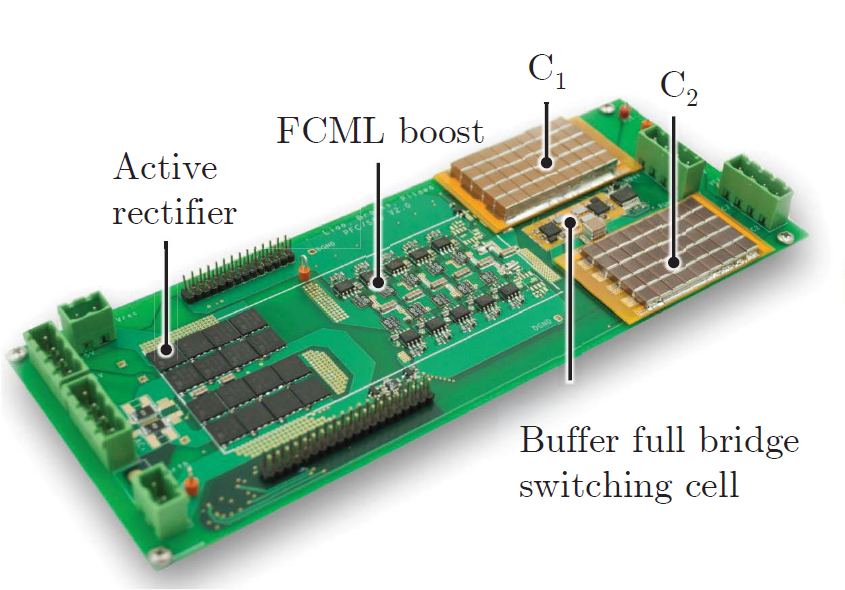

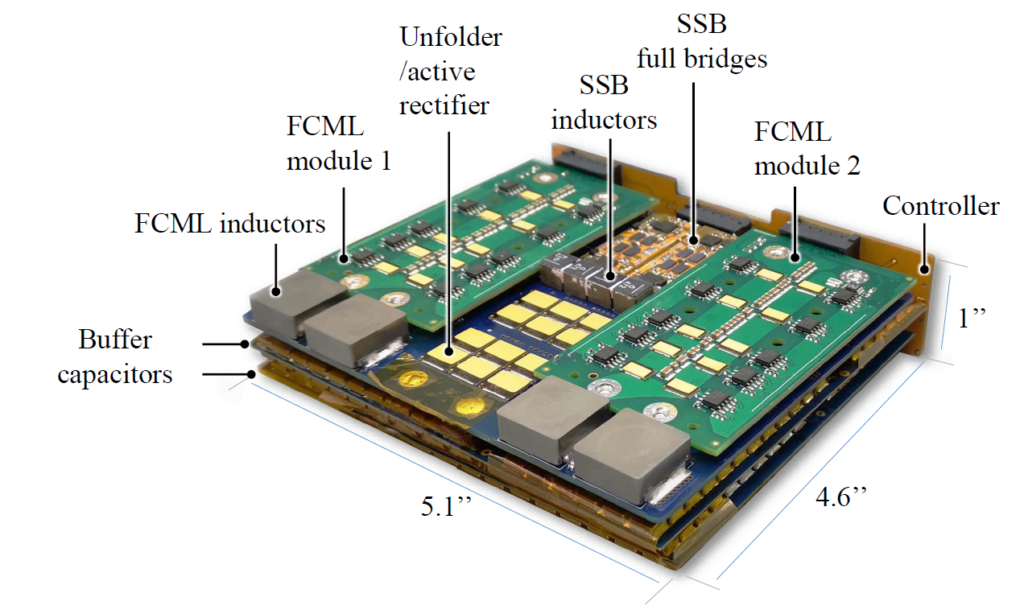

90-265Vac-to-400Vdc 1.5 kW ac-dc power-factor-correction rectifier – 2018

Ac-dc converters are essential for applications such as data center power delivery, EV chargers and so on. The ac-dc converter features a multi-level boost converter for power factor correction and a series-stacked buffer (SSB) for twice-line frequency power buffering. The multi-level boost converter reduces the size of the input inductor size, while the SSB reduces the required buffer capacitor size. Together, the system efficiency and power density are extremely high. It also requires innovative control to couple the PFC and SSB.

Read more: personal version of ECCE2018, JESTPE2020

Official IEEE publications: ECCE2018, JESTPE2020

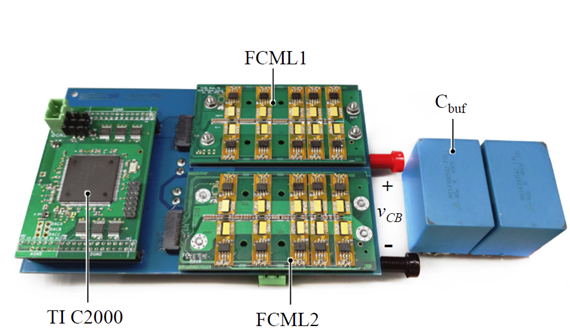

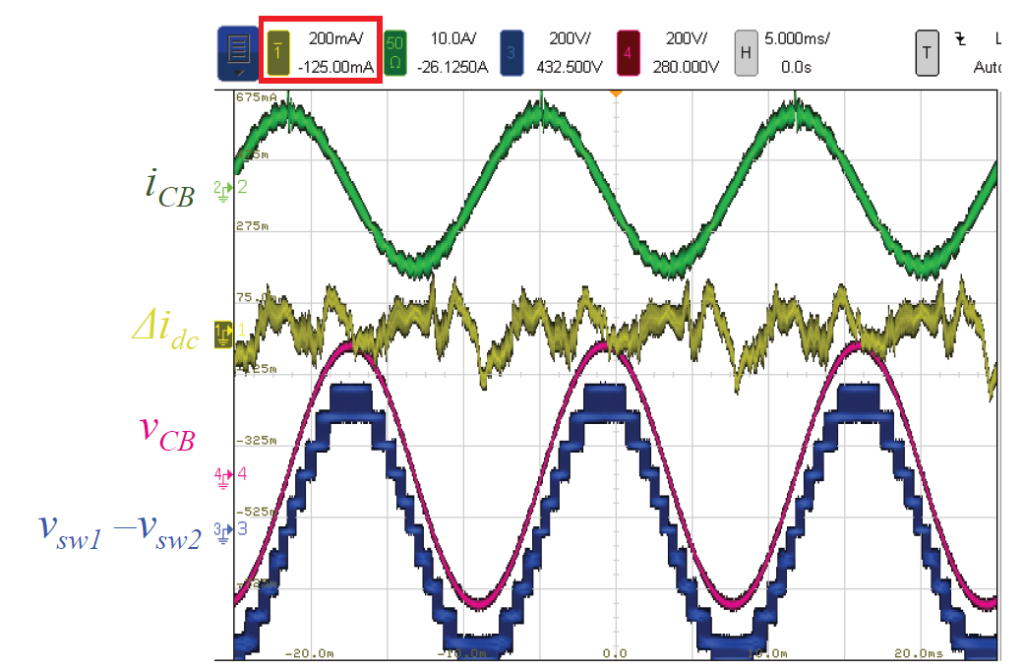

Bipolar multilevel active buffers – 2019

In single-phase ac-dc/dc-ac conversion, there’s a twice-line frequency power mismatch between the ac and dc side. Usually, a large dc-link capacitor at the dc-bus is used to buffer the mismatched ripple power. Yet the size of the capacitor is big because of the tight dc-bus voltage ripple requirement. In this work, an active multilevel full bridge converter is used to fully charge and discharge the buffer capacitor so the size is much reduced, for 2 kW, 400 V single-phase conversion. The capacitor size is reduced by over 20 times than conventional electrolytic capacitor bank solution.

Read more: personal version of APEC2020

Official IEEE publications: APEC2020, TPEL2021

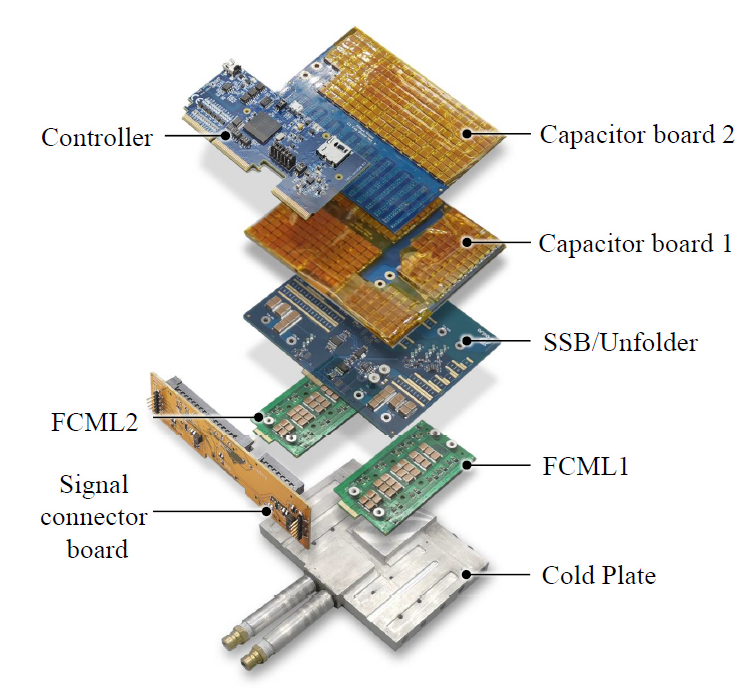

6.6-kW single-phase on-board EV charger funded by ARPA-E – 2019

The 6.6 kW EV charger is funded by ARPA-E CIRCUITS program. Using FCML and active buffer, it achieved record breaking power density of 201 W/cm^3 with advanced cold plate for liquid cooling

Official IEEE publication: APEC2021

Undergrad Projects:

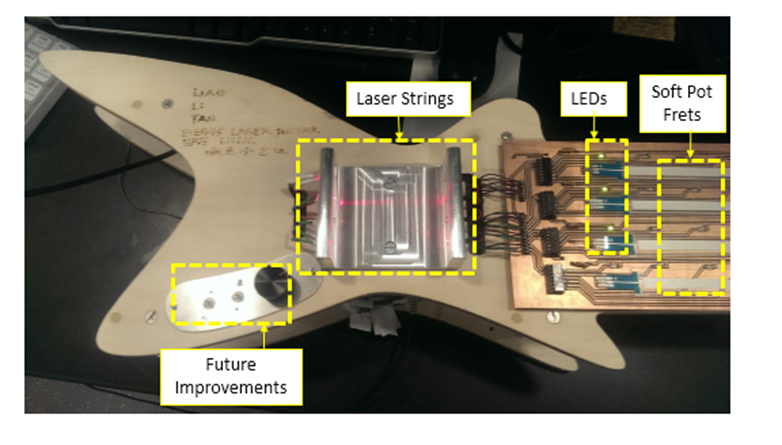

UIUC senior design project – 2015: Laser Guitar With Instructional LED Display

Formula SAE project – 2012: Illini Formula Hybrid SAE 2012 Carbon Fiber Body